# A Spice-2 Subcircuit Representation For Power MOSFETs Using Empirical Methods

Application Note

October 1999

AN9209.2

### Abstract

An accurate power-MOSFET model is not widely available for CAD circuit simulation. This work provides a subcircuit model which is compatible with SPICE-2 software and MOSFET terminal measurements. SPICE-2 is the circuit simulation package of choice for this work because of its universal availability, despite its inherent limitations. These limitations are circumvented through circuit means.

This effort models power-MOSFET terminal behavior consistent with SPICE-2 limitations; hence it will differ from the physical model as suggested by Wheatley, et al<sup>1</sup>, Ronan et al<sup>2</sup> and others. We feel we have advanced prior efforts<sup>3</sup> particularly in areas of third-quadrant operations, avalanche-mode simulation, switching waveforms and diode recovery waveforms.

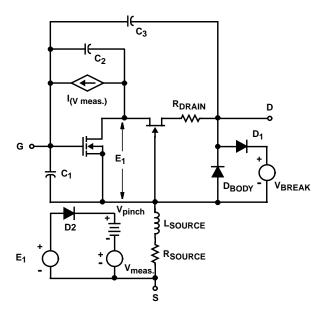

#### FIGURE 1. SPICE-2 SUBCIRCUIT FOR POWER MOSFET SIMULATION

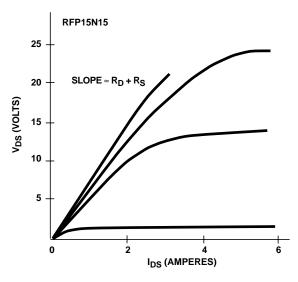

NOTE: If the JFET source voltage,  $E_1$ , is very low relative to its  $V_{PINCH}$  voltage, the JFET is in a highly conductive state, tightly coupling  $C_2$  to the JFET drain. However, as the voltage  $E_1$  approaches  $V_{PINCH}$ , the JFET operates in a constant-current mode, thereby permitting a much faster drain slew rate, which is determined primarily by  $C_3$ .

## Discussion

The subcircuit shown in Figure 1 is described in Table 1. All passive circuit elements are constants. The very-high-gain JFET is used to simulate the dual-slope drain voltage vs time switching curve common to the power MOSFET.<sup>1,2</sup>

If E<sub>1</sub> exceeds V<sub>PINCH</sub>, errors will exist in the turn-on waveforms. The C<sub>2</sub> discharge current-controlled current source remedies this situation in conjunction with the subcircuit containing D<sub>2</sub>. The D<sub>2</sub> ideality factor was set at 0.03 to assure that E<sub>1</sub> minus V<sub>PINCH</sub> does not exceed several millivolts.

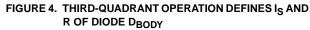

The body diode cannot be properly modeled by the JFET gate-drain diode, hence  $D_{BODY}$ . Conditions of Table 1 assure that most third-quadrant current flow is via  $D_{BODY}$ . Avalanche breakdown is more accurately modeled by the clamp circuit containing  $D_1$ .

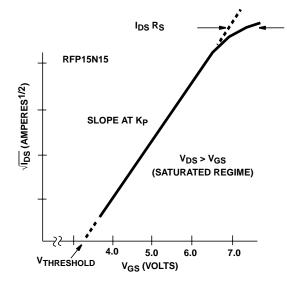

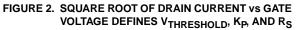

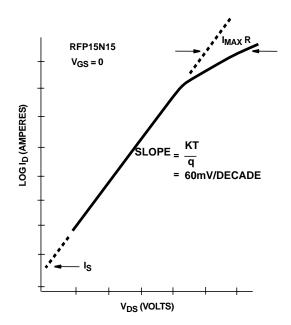

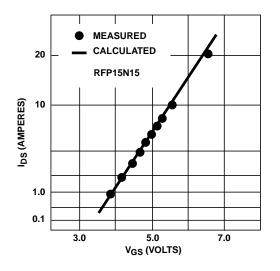

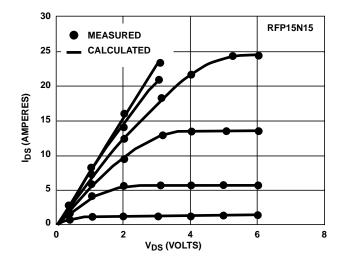

Table 1 in combination with Figures 2, 3, 4 and 5 provides the required empirical inputs. Table 2 lists the preferred algorithm for parameter extraction.

| TABLE 1. EMPIRICAL INPUTS |                                                                                                                                                                                                                             |

|---------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MOSFET                    | Enhancement mode; W = L = 1 $\mu$ m; K <sub>P</sub> (Figure 2); V <sub>TO</sub> (Figure 2); C's = 0; I <sub>DSO</sub> = IE -12                                                                                              |

| JFET                      | Depletion mode; areas factor = 1; B = $100K_P$<br>(Figure 2); V <sub>TO</sub> = V <sub>PINCH</sub> (Figure 5); C's = diode<br>lifetime = R <sub>SERIES</sub> = 0; diode ideality factor =<br>1.0, I <sub>DSO</sub> = IE -20 |

| BODY DIODE                | $    I_S \mbox{ from Figure 4; Ideality Factor = 1.0; R from Figure 4 (must be very much greater than R_D); C (from C_{OSS}); lifetime = best fit to T_{RR} $                                                               |

| D <sub>1</sub>            | $I_S$ = arbitrary; C = lifetime = 0; ideality factor = best low-current fit; R = best high-current fit                                                                                                                      |

| D <sub>2</sub>            | $I_S = 1E -8$ ; C = lifetime = R = 0; ideality factor = 0.03                                                                                                                                                                |

| R <sub>S</sub>            | Figure 2.                                                                                                                                                                                                                   |

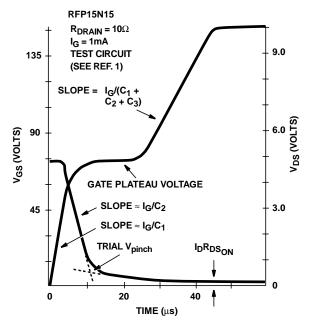

| R <sub>DRAIN</sub>        | Figure 3.                                                                                                                                                                                                                   |

| L <sub>S</sub>            | Approximately (5L) In (4 L/d) nH; L and d are source wire inches.                                                                                                                                                           |

| V <sub>PINCH</sub>        | V <sub>TO</sub> of JFET.                                                                                                                                                                                                    |

| V <sub>BRK</sub>          | Avalanche voltage.                                                                                                                                                                                                          |

| C <sub>1</sub>            | From Figure 5.                                                                                                                                                                                                              |

| C <sub>2</sub>            | Maximum from Figure 5.                                                                                                                                                                                                      |

| C <sub>3</sub>            | Minimum from Figure 5.                                                                                                                                                                                                      |

#### TABLE 2. PREFERRED ALGORITHM FOR PARAMETER EXTRACTION

- 1. Determine K<sub>P</sub> of lateral MOS

- 2. Determine V<sub>TH</sub> of lateral MOS

- 3. Determine C<sub>1</sub>

- 4. Determine  $C_1 + C_2 + C_3$

- 5. Determine R<sub>DS</sub>

- 6. Assign B of JFET = 100 x K<sub>P</sub> of lateral MOS

- 7. Use trial VPINCH

- 8. Use C2 (Maximum), C3 (Minimum) are curve-fit C's

2

9. Adjust V<sub>PINCH</sub> to fix gate voltage plateau

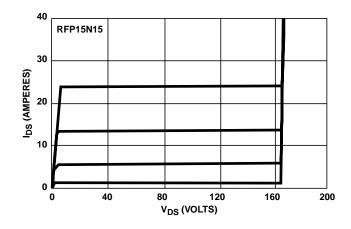

FIGURE 3. DRAIN CURRENT vs DRAIN VOLTAGE WITH CONSTANT GATE VOLTAGE DEFINES "ON" RESISTANCE

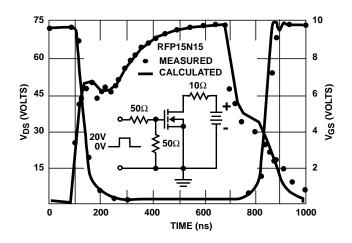

FIGURE 5. DRAIN AND GATE VOLTAGE vs TIME DETERMINE  $C_1,\,C_2,\,C_3$  AND  $V_{\mbox{PINCH}}.$

### Results

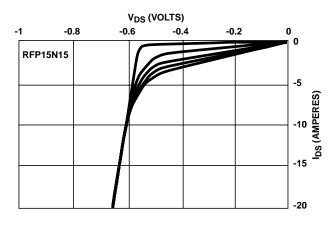

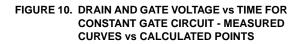

Figure 6 and Figure 7 compare measured static data to calculated transfer curves and output curves. Calculated static-output curves are shown in Figure 8 and Figure 9 for third-quadrant range, including avalanche.

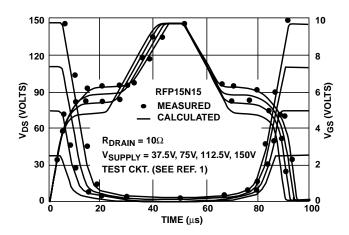

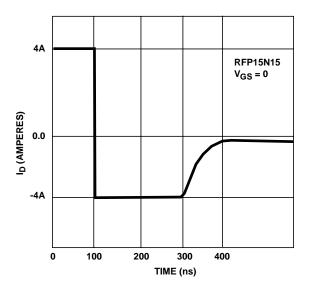

Calculated switching data is compared to measured switching curves<sup>1,2</sup> in Figure 10 and Figure 11. Calculated body-diode recovery curves are shown in Figure 12.

FIGURE 6. DRAIN CURRENT vs GATE VOLTAGE (NOTE SQUARE ROOT SCALE) - MEASURED CURVE vs CALCULATED POINTS

FIGURE 8. THIRD-QUADRANT DRAIN CURRENT vs DRAIN VOLTAGE WITH CONSTANT POSITIVE GATE VOLTAGE (CALCULATED)

FIGURE 7. DRAIN CURRENT vs DRAIN VOLTAGE FOR CONSTANT VALUES OF GATE VOLTAGE -MEASURED CURVES vs CALCULATED POINTS

FIGURE 9. FIRST-QUADRANT DRAIN CURRENT vs DRAIN VOLTAGE,  $V_{GS}$  = CONSTANT. NOTE AVALANCHE BREAKDOWN (CALCULATED)

FIGURE 11. DRAIN AND GATE VOLTAGE vs TIME FOR STANDARD SWITCHING CIRCUIT - MEASURED CURVES vs CALCULATED POINTS

FIGURE 12. THIRD-QUADRANT DIODE - RECOVERY vs TIME CURVE (CALCULATED)

# Conclusion

An equivalent-circuit model for power-MOSFETs, that is suitable for use with the SPICE CAD program, has been demonstrated. The model is compatible with all versions of SPICE presently available without modification to the program's internal code. The model addresses static and dynamic behavior of first and third-quadrant operation, including avalanche breakdown, and is empirical in nature. All necessary input parameters may be inferred from data sheets or simple terminal measurements.

Excellent agreement has been obtained between measured and simulated results.

### References

- Wheatley Jr., C. F. and Ronan Jr., H. R., "Switching Waveforms of the L<sup>2</sup>FET: A 5-Volt Gate-Drive Power MOSFET," Power Electronic Specialists Conference Record, June 1984, p. 238

- [2] Ronan Jr., H. R. and Wheatley Jr., C. F., "Power MOS-FET Switching Waveforms: A New Insight," Proceedings of Powercon II, April 1984, p. C-3

- [3] Nienhaus, H. A., Bowers, J. C., and Herren Jr., P. C., "A High Power MOSFET Computer Model," Power Conversion International, January 1982, p 65

All Intersil semiconductor products are manufactured, assembled and tested under ISO9000 quality systems certification.

Intersil semiconductor products are sold by description only. Intersil Corporation reserves the right to make changes in circuit design and/or specifications at any time without notice. Accordingly, the reader is cautioned to verify that data sheets are current before placing orders. Information furnished by Intersil is believed to be accurate and reliable. However, no responsibility is assumed by Intersil or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Intersil or its subsidiaries.

For information regarding Intersil Corporation and its products, see web site www.intersil.com